# コンピュータアーキテクチャ

# コンピュータシステムの内部構造を 分かりやすく解説

コンピュータアーキテクチャは、コンピュータの設計・構成方法に関する学問です。狭義には、コンピュータのハードウェアとソフトウェアの境界を扱います。コンピュータアーキテクチャの理解は、現代社会におけるデジタル化とテクノロジーの進化に対応するために非常に重要です。

この講義では、近年注目を集めているオープンソースのアーキテクチャであるRISC-Vに焦点を当てます。講義では、コンピュータの発展の歴史や基本構成から始まり、RISC-Vの命令セットアーキテクチャ、RISC-Vプロセッサの設計と評価、機能拡張などを理解することを目指します。実践的なハンズオンも取り入れながら、コンピュータシステムの内部構造を分かりやすく解説します。

## 特徴

## CPUの内部動作を学ぶ

どのように命令が定義され、命令を実 行するためのハードウェアをいかに設 計し、実行されるのかを学びます。

## 特徴2

### CPUの実装

必要に応じて、FPGAデバイスへの RISC-V実装にも取り組み、その動作を 確認します。

## 学習時間

#### 対象者

中級レベル

**発展** レベル

### 開催場所

貴社指定場所 (応相談)

## 講師プロフィール

## 江川 隆輔

東京電機大学工学部情報通信工学科教授

東北大学大学院情報科学研究科情報基礎科学専攻博士後期課程修了(2004年)、博士(情報科学)取得。東北大学等を経て. 2020年より現職。東北大学サイバーサイエンスセンター客員教授、産業技術総合研究所デジタルアーキテクチャ研究センター客員研究員を兼務。

東京電機大学では「コンピュータアーキテクチャ」を軸として、高性能計算システムとシステムソフトウェアに関する研究に従事。

\ 講師についてもっと詳しく /

https://researchmap.jp/read0121311

# プログラム

- 1. はじめに (コンピュータの歴史)

- 2. RISC-Vの概要

- (1) RISC-Vの概要とオープンソースアーキテクチャの重要性

- (2) RISCとCISC

- (3) RISC-Vの命令セットアーキテクチャの特徴と基本命令

- 3. レジスタとアドレッシング

- (1) RISC-Vのレジスタセット

- (2) メモリアドレッシングモード

- 4. RISC-Vの設計

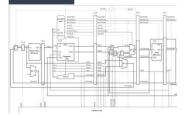

- (1) RISC-Vプロセッサの基本ブロックとデータパス

- (2) コントロールユニットの設計と制御信号

- 5. パイプライン処理

- (1) RISC-Vプロセッサのパイプライン処理の基本

- (2) パイプラインハザード

- 6. RISC-Vの動作

- (1) RISC-Vアセンブリ言語の基本構文と命令の実行例

- (2) プログラムの開発と実行(ハンズオン)

- 7. RISC-Vの拡張

- (1) RISC-Vアーキテクチャの拡張

- (2) 拡張命令の追加

本講義内容・時間はご提案です。

実際には、ご希望をうかがった上で、内容や時間など 御社に最適なプログラムとなるようカスタマイズいた します。

ご質問・お申し込みは、お気軽に担当者または右記窓口までご連絡ください。

## お問い合わせ窓口

## 東京電機大学 リスキリング事務局

$\mathsf{E} \mathsf{X} - \mathcal{N} : \mathsf{information-tdudtec@jim.dendai.ac.jp}$

電 話:03-5284-5202 (学長室内)

(3営業日を目安にご連絡いたします)